1、首先打开已经编译通过的原理图,选中工程文件。

2、点击Tools>>Create Netlist指令。或者直接点击工具栏中次指令。

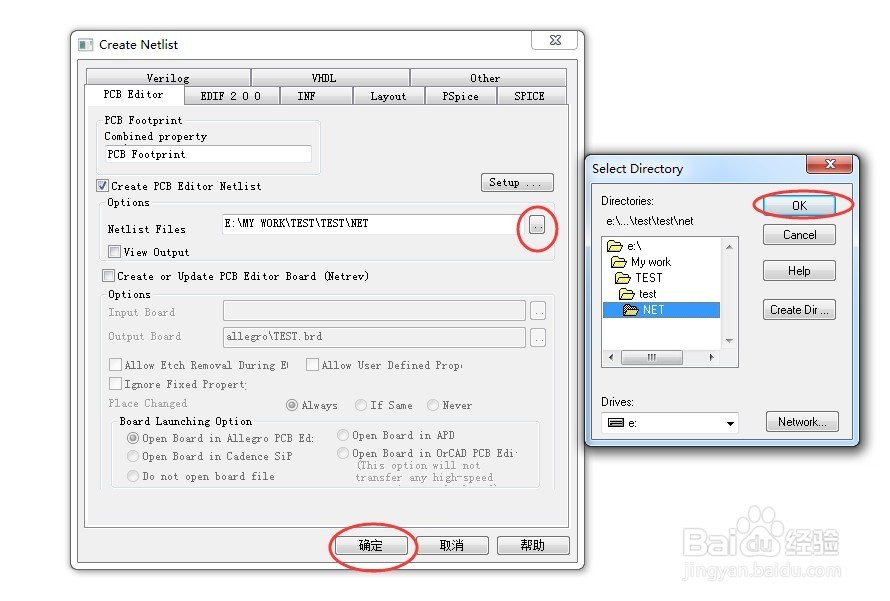

3、弹出窗口后,请点击到PCB Editor,点击选择保存网表的路径,选好路径后点击OK,然后点击确定后会提示是否导出网表,点击确定即可。如果导出出错,请确认原理图编译通过,所有器件都已经选好封装等等。

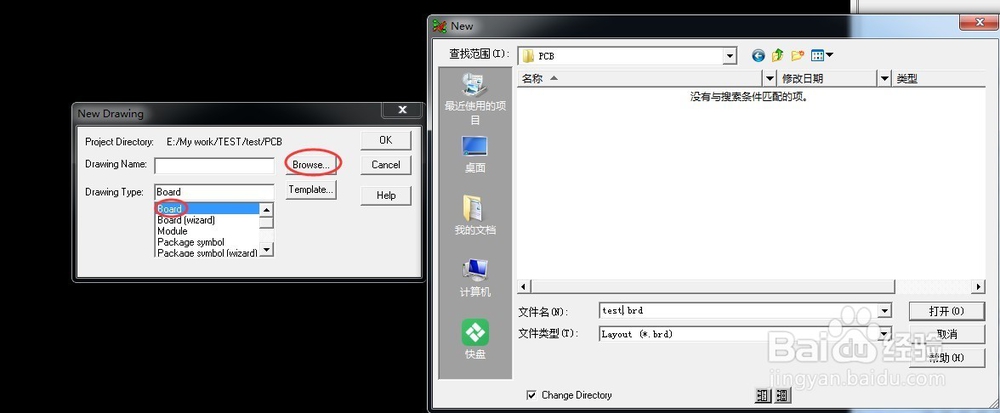

4、打开Allegro,新建一个PCB,并指定好PCB文件的保存路径,之后点击OK。

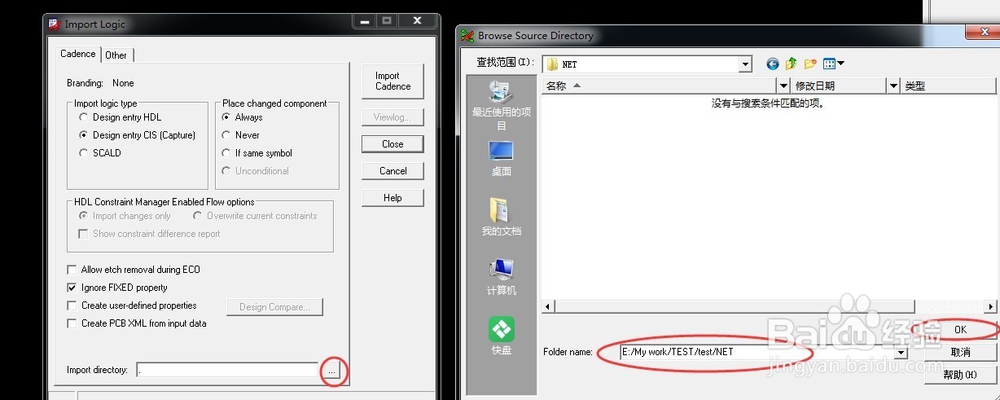

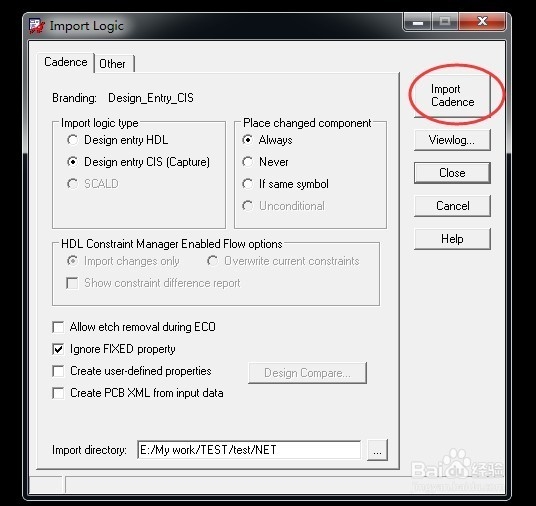

5、点击File>Import>Logic,弹出以下窗口,勾选以下选项。

6、选择网表的路径,点击OK。

7、可以看到网表的路径已经选好,点击Import Cadence导入网表,到此网表导入完成。