CASE变成CASEX再加上default:y=1'b0就可以解决此问题,使用方法。

如下参考:

1.首先,右键单击项目并单击NewSour艘早祓胂ce以创建一个新的代码文件。

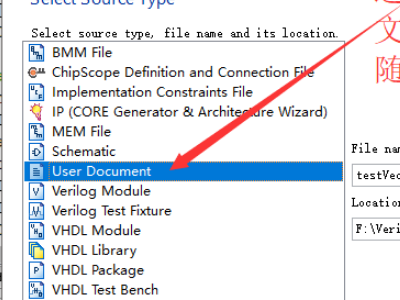

2.选择用户文档创建一个自定义文档文档,文件名和后缀随意。

3.创建完成后,切换到文件面板底部,双击打开文件,根据自己喜欢的形式输入数据。

4.写完数据文件后,右键单击项目,单击NewSource,然后选择Verilog测试装置,输入文件名并继续,选择要测试的模块,然后创建文件。

5.双击打开文件,可以看到要测试的模块块的输入对应一些reg寄存器类型,输出对应一些wire类型。添加两个参数常量,然后为for循环添加计数变量J,并添加一个向量数组来保存文件读取的数据。

6.下面是程序生成的用于实例化和连接接收测试模块的代码。只需编写end之间的测试代码。